3.5.6. Counters, Interruptions (IRQ) |

For computer work is necessary to generate a clock signal, which period may operate the program. For this purpose, a PC has a programmable three-channel generator.

Triple programmable timer over the canal '0' ensures accurate clock for an hour, the second counter across the channel '1' to control the switching DMA controller, and the third over the counter channel '2' gives the tone a small speaker in the casing.

Each of the counter has a separate entrance to the stroke that leads to the main signal from the microprocessor clock generator, which was then under the control of the program multiplies or divides in each counter. Counters related to the data and address bus part, in order to be able to enter new content into their registers or read data from them, and the relationship has changed over the of address timer mode, a total of 6 modes work; counting backward, forward, program controlled initial state and other.

The work incorporates a microprocessor controller interrupts (two controllers a total of 16 required to end) with their signal processor draws attention to a phenomenon on the basis that the computer decides what should work and that routine, mostly from the BIOS to accomplish. This method avoids the appearance of a continuous monitoring of the computer (polling) and the acceleration of the system. An example is the keyboard, which on average is rarely used. If you press a key is generated interrupt signal (Interrupt request - IRQ) and sends a request to execute a computer program routine for the keyboard and also computer generated at specified intervals to establish a state of fine keyboard.

Signal to interrupt the microprocessor indicates that some of the I / O device requires attention. When the microprocessor receives an interrupt request stops further execution of the current operation and stores in its registers the position at which the current action aborted. Then running the routine interrupted ISR (Interrupt Service Routine). You will perform routine program knows the number of interrupts that gets a response in the form of binary number of 2-byte and when to address the device, which required termination. The data entered in the first 1024 bytes of random access memory (Table interruption) enrolled 256 addresses in sequence of 4 bytes, and the processor as the number of interruptions seek 7116 113th place since the beginning of the list and execute program routine start address which is listed at 113 place. Home address ISR is called interrupt VECTOR. By performing the software routines interrupted processor reads from its register the position in which the current operation was interrupted and continues its execution.

As more peripherals may require interruption, introduced the concept of priority interrupts, so that in case of multiple simultaneous requests to end the first executes the one that has the highest priority and that is fine with the lowest number.

Interruptions are divided by type into three groups:

1. Interruptions to the default memory locations (BIOS DOS). 2. Programming disruptions created by the user. 3. Circuit interruptions, which can allow/deny.

The microprocessor has two inputs for interruptions:

I. Input for non masking hardware interrupts. II. Maskable interrupt input for hardware systems through who is making the request for program termination.

Not maskable interruptions, directly affect the processor, resulting dividing by zero error in memory when checking parity or transmission through the I / O channel. Have the highest priority in execution.

Masking (hardware device) interruptions is achieved additional devices in the computer and managed INTERRUPT CONTROLLER. Controller interrupts analyzes interruption by priority, signals the microprocessor interruption highest priority when it approves a microprocessor, controller interrupts sets the number of data bus termination (0-255) that upon the acceptance of interruption control sends peripherals. Microprocessor apparent number of interruptions and breaks from the table reads and executes the interrupt vector corresponding ISR.

Additional devices are connected to the bus through a lengthy multiple contact connector in the form of a slot into which is inserted a printed circuit board (card) on which the device is designed hardware device such as disk controller, fax/modem or network card. All slot-these are connected with buses on the motherboard and cables that allow you to send the signal to stop (not the number of interruptions).

Hardware interruptions generate basic and additional control, the first controlled interruptions of 0-7, and the second from 8-15 but through another port base, as shown in Table interruption ranked by priority, starting from the highest priority to the lowest.

|

| Table 3.5.16 Hardware interruptions of PC-AT configuration. |

Usually IRQ10 and IRQ15 available for general upgrade, although it can also be used IRQ5, IRQ11 and IRQ12 if the devices for which they are intended not incorporated. Some of the technology, as IO APIC (I / O Advanced Programmable Interrupt Controller), with an appropriate motherboard and operating system such as Windows XP or Linux, give support multiprocessor computers and is used to send additional required interrupts to different CPUs and between themselves . In addition to the foregoing, PCI-IRQ interrupt - PIRQ (16-23) may be sent through the system for USB, SATA and PCI-Express devices, with no overlap with the standard IRQ system (0-15). PIRQ is basically an extension of the previous table. The processor incorporates a Local APIC that can support up to 224 usable IRQ required for communication up to 60 processors. Listed technology firm uses Intel Pentium processors, and there are functionally similar versions from other manufacturers (such as OPEN Programmable Interrupt Controller).

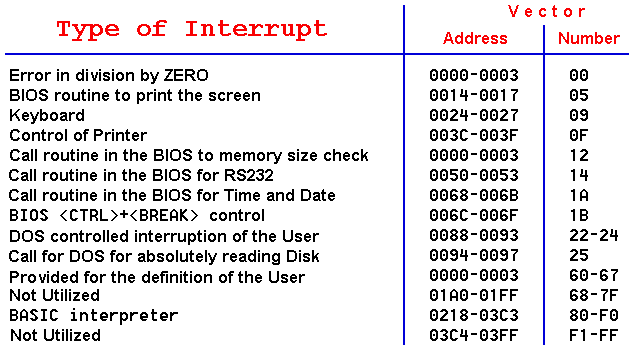

Interruptions require hardware components of a computer, which basically operate independently but require processing by the microprocessor when requesting termination. All circuits of the same type to seek a break from the previous table, for example, for all discs will be the same interrupt number to IRQ14 and is reported as the presence of interruption control signal at 'fourteenth wire - IRQ14' of interrupt bus. Part of other vector interrupts, which are not part of the computer hardware structure is shown in Figure 3.5.17.

|

| Table 3.5.17 Vector interrupts of PC-AT configuration. |

If during the execution of a tip breaking new higher priority interrupt, the currently active termination, execute higher priority, then continuing the interrupt program, and at the end of the current program.

There are software interruptions generated by the program in order to summon some additional applications for execution. Programming disruptions can have a number in the table vector interruption using already defined numbers and routines DOS and BIOS, and will define a new break that is not 'busy' in the table which termination will be given a routine created by users. So with pressing the keyboard realizes fine IRQ1 and run the program on 4 byte address entered at 24-27 in the BIOS. Four addressed passages (ports) for computer hardware. If you create a new interrupt number and its associated program and join the cease-IRQ1 may be amended with the new program layout of letters keys on the keyboard, or change to a new program with the keys in relation to where the program has the original cutoff.

DMA, controller interrupts, I / O controller, keyboard controller, and other logic circuits form a group of electronic circuits commonly integrated into a larger single chassis called ASIC (Application Specific Integrated Circuit) or CHIPSET. Some motherboards have in their composition of integrated circuits that are usually performed as peripheral cards such as hard disk controller, serial and parallel control channels and the like. It is almost the rule in all PCI motherboards. Design and organization chipsets are of fundamental importance to the quality and performance of the entire computer system.

The concept of BIOS at PC dates back to the 80's when they designed the first PC. With time, it is shown that there are limitations with regard to the addition of computer hardware, and is already in the beginning implemented an additional controler of hardware interrupts. But the big problem was the large server resources. Modern devices are very different in interfaces and applications, and in approximately the 2005th year, the company Intel introduced a new concept of EFI (Extensible Firmware Interface) as a BIOS upgrade. Based on EFI specifications is established UEFI specification (Unified Extensible Firmware Interface), an intermediate layer between the BIOS and the operating system, which was accepted by almost all manufacturers of computers and computer equipment, and have solved many existing restrictions such as: the variety of operating systems, the size of the CPU address space and variety of performances (x86, x86-64, ARM), access to large disk resources (MBR-GPT) and others. As importantly is introduced the 'boot manager' mechanism which is responsible for loading the operating system and all the necessary drivers, and important is ability of upgrades. So began with the servers and with time become an industry standard for home computers with any Windows, Linux or Mac operating system.

|

Citing of this page: Radic, Drago. " Informatics Alphabet " Split-Croatia. {Date of access}; https://informatics.buzdo.com/file. Copyright © by Drago Radic. All rights reserved. | Disclaimer |