3.5.4. Working (main) Memory |

RAM (Random Access Memory) is a working computer memory, random access memory, or the program will not be invited to enroll in re-loading the same memory location, because in the meantime, some of them occupied by another task. RAM is not able to remember the content of a long, except in special technological designs - SRAM (Static RAM), and through the DMA circuitry performs update (renewal) for retention of content. Hence the name of DRAM (Dynamic RAM). Refreshing memory takes about 5% of the time in the communication between the individual components computers. Size of memory is of great importance to the usability of computers. RAM chips are inserted into special slots provided for it, each of which usually represents a 'memory bank' or more grooves with chips form a single bank. Common designation Module SIMM (Single In-line Memory Module) with mostly 30, 72, 144, 168 or 240-pin module to this connector in the slot, depending on the version and type. Logical organization of access modules is performed by 'banks'. The memory is divided into banks and each of the memory banks may include one or more modules. It is important that the bank must be 'full', or if it is provided that the bank includes two slots, both of them need to be 'filled' with modules. The computer will work if there is at least one 'charged' bank.

Access memory organized as retrieval of a memory cell in a matrix of rows and columns and before the data should reach RAS signal line (Raw Address Strobe) and column CAS (Column Address Strobe) determine that the cell in question and only then is it possible to read the contents . DRAM is lost by reading the content and before 'leaving' cell content must re-enroll. Time needed to determine the column and row and retrieval of information is called the access time (access time) and is usually from 7 ns to 70 ns for DRAM, and less than 1 ns for SRAM. Time of access to the DRAM and time again to add data entry and gain CYCLE duration of memory.

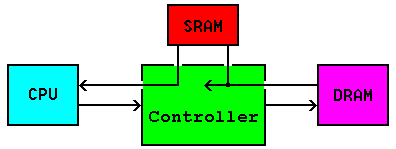

How much SRAM is more expensive than DRAM, but also faster, DRAM is used as a working memory for processing, and as a fast SRAM cache memory which is used for internal microprocessor acts as a temporary storage of data while not allowing access to the slower DRAM, and is used as a buffer in communication with a permanent memory (hard disk, etc.).

|

| Figure 3.5.10 Principle of the controller cache. |

Distribution of the SRAM, DRAM and microprocessor controller performs cache. A similar principle can be used to accelerate reading and writing data to the hard disk. But if the client software does not recognize whether the data stored in the cache memory or on the hard drive and not made a timely save from the cache to the disk may cause the loss of data after the end of the program. Therefore, the system is well organized in a way that the buffer cache operates only in the process of reading data from the hard disk.

Example IV

Electronic version of ROM in the diode and MOS technology.

|

| Figure* 3.5.11 Matrix ROM performed in diode and MOS technology. ( + / - ) |

Diodes are electronic components that conduct current in the direction of 'A=>K', in the direction of 'K=>A' not implemented. The letters 'A' and 'C' are the initial letters of the diode electrodes (anode, cathode). If the microprocessor, the Address Decoder voltage sent to the address line, the voltage will appear only on those lines that are reading through diodes connected to address live wire. On reading the lines appear binary combination of 'power' that corresponds to one of the of address live cables.

One can not simultaneously address the multiple lines of address but must be done by reading the content line by line (address by the address). If it were up to eight lines of reading them to appear different eight-bit combinations of voltages depending on the address, and the combination of diodes.

Similarly behave MOS elements which grounded line readings if the voltage appears to address line. Principle of MOS transistors is easiest to visualize as a valve operation conducted in the direction of 'S=>D' under the control voltage to the electrodes 'G'. Case 'S', 'D' and 'G' are the initial letters of the MOS transistor electrodes (source, drain, gain).

In designing a serial PROM with diode (or MOS transistor) sets hotmelt connection that using fillers interrupted at places in order to get the proper code combinations for certain address lines.

In a similar way to organize and matrix RAM except that the opportunity to read and write under the control of one or two water web address for each memory element. Although the memory can manufacture different technologies of MOS technology, none of them give so little power consumption and the number of elements in the volume. Almost all computer circuits made in a kind of MOS technology.

Example V

Electronic version of SRAM (Static RAM) memory cells.

|

|

| Figure* 3.5.12 Memory element of SRAM. ( + / - ) |

Memory power supply allows the transistors 'T3' and 'T4' which are associated with its own entrance and exit to each other so they are coming out with resistance 'R' always opposing levels. Basically it's about the application of Flip-Flop. In this way, one realizes that the transistor leads and the other does the water supply by maintaining the condition are mutually supportive. Restoring one output to the input of the second transistor is electrically achieved positive feedback, which helps state change initiated by the individual transistors and therefore the switching transistors from one state to another (implemented - not implemented) is quite fast because it is essentially the process of transferring cumulative. State of both transistors can be changed only by external influences. Editing is done so that the address line entry and reading (W - Word line) to enable the implementation of transistors 'T1' and 'T2', and over the waters of enrollment (BL - Bit line) will set the voltage levels (0 or 1 symbolically) to be 'T3' to accept. 'T4' will automatically take the opposite position than the 'T3'. Couple 'T3' and 'T4' will retain the current state until a power supply (+U) and while it does not lead to 'T3' voltage level opposite him.

So, an essential storage element for static ram is state of transistor ('T3' and 'T4'). Reading the situation is similar. The voltage at the address water will allow transistors to implement 'T1' and 'T2' and that the level of 'T4' transfer to line readings (non-BL) and then on one of the lines of data bus.

Thus, the memory cell stores a condition that is stored there until a source of energy or until the situation has changed. How to read the cables separated from the power entry now can be read by any change in the memory cell, contributing to a higher overall speed.

Example VI

Electronic version of DRAM (Dynamic RAM) memory cells:

|

|

| Figure* 3.5.13 Memory element of DRAM. ( + / - ) |

An essential storage element of this memory cell is the charge on the capacitor 'C'. The voltage at the address water will allow the implementation of transistors 'T' and the over water entering and reading (BL) been charged capacitor 'C'. If the state wants to read through the condenser water entering an address and reading (W) will enable the implementation of transistors 'T' and the charge on the capacitor 'C' raises the water entering and reading the voltage difference. As the capacitor discharges when it needs to rebuild its charge (preCharge), or re-enter the content. But as the charge on the capacitor cells regardless of the reading time is necessary to loose at regular intervals to make the REFRESH contents of the entire memory. To capacitor 'C' shoves it takes some time, as this type of memory seems to be considerably slower than the SRAM type memory several orders of magnitude, but also much cheaper as compared to the SRAM needs a lot fewer elements to create one memory cell.

DRAM performance such as Rambus DRAM - RDRAM and Synchronous DRAM - SDRAM peculiarity to have supervised chipsets operate in synchronization with an external microprocessor bus - FSB (Front Side Bus) and accelerates the exchange of data between the microprocessor and them. SDRAM is a type of memory that the DDR (Double Data Rate) performance of works under the principle of reading the state of the cell several times higher clock speed of the bus. They are available in versions DDR1 (200-550 MHz), DDR2 (500-1066 MHz), DDR3 (800-1600 MHz) and DDR4 (>1600 MHz), has been developed to increase the operating speed to memory speed reading equal to external FSB bus speed microprocessors. Moreover each subsequent series works with lower operating voltages and thus lower consumption. Consumption depends directly on how much memory chip's built-in memory module. The memory capacity of the modules is very diverse and depends on the type of memory module and opportunities chipsets. The motherboard documentation states what modules must be, and how much, and how they can be used.

It is worth noting that DRAM memory modules used in computers and meant for general non-ECC type. According to Figure 3.5.13b missing one chip to control the parity of enrollment or the read data from memory location about correcting errors (error correcting code memory). In fact, depending on the content of the data for entry in the ECC memory adds them to "0" or "1" before writing data to a memory location, which is kept in an extra chip, so that the total number of units was zero or even (parity check), and that condition controls when reading the memory location. However, additional chip raises the module and control circuits are more complex. Accordingly, the ECC memory modules are mainly used in servers. What type of modules supported by the motherboard should be checked by examining in its documentation.

SUMMARY:

Thus, WORKING MEMORY (WM) used the computer to load the data into it and / or program support (software) from the slow permanent memory and microprocessor uses them in his work. From the above it is clear that the content stored in working memory is constantly changing. Basically working memory is DRAM type, which is easier to produce and therefore less expensive, and with respect to the acceleration data entry in her individual circuits and devices used by the computer capacity considerably smaller but fast SRAM cache type, to create more complex and more expensive.

So as to prevent overflow of working memory for example, with the huge size of data (such as images), operating systems typically are designed to be part of the permanent memory is declared as working memory. That part is called VIRTUAL MEMORY (VM) and is implemented as a separate disk partition (SWAP partitions in Unix-Linux OS) or as file (PAGEFILE.SYS file in Windows OS). OS does not necessarily have to use this type of memory.

Today's working memory cheaper than formerly, when the cost price as everything else in the computer, and if it has enough of working memory, by software part of WM can be convert to the RAM-Disk which the whole or a one part can be used as virtual memory. Higher working memory capacity allows to use smaller capacity of virtual memory. It is used relationship WM:VM = 1:1.5 or higher, while today it is contrary. If the OS is designed to use virtual memory, but if working memory of DRAM type is available enough, virtual memory should be realized in a smaller size but not completely eliminate.

|

Citing of this page: Radic, Drago. " Informatics Alphabet " Split-Croatia. {Date of access}; https://informatics.buzdo.com/file. Copyright © by Drago Radic. All rights reserved. | Disclaimer |